15 V 至 350 V 范围的氮化镓 (GaN) 异质结场效应功率晶体管已在电源转换、电机驱动和激光雷达脉冲光等应用中得到验证。在效率、尺寸、速度和成本方面比硅具有显着优势。这些优势是由于临界电场比硅高一个数量级,特别是带隙优势为 3 倍,电子迁移率优势为 1.3 倍。

由此产生的器件开关速度更快、物理尺寸更小、RDS(on) 更低,并且可以承载更高的固有电流[1]。当今大多数 GaN 晶体管 都具有横向结构,允许将许多晶体管经济高效地集成到单个衬底上,如图 1 [2] 所示。

图1.

显示 GaN 集成电路 构建模块的横截面。图片由 Bodo 电力系统提供

分立器件 栅极驱动器 器件

每个功率晶体管与栅极 驱动器 紧密配合,作为 电力电子器件 开关 转换器 的基本构建块。导通时,栅极驱动器从去耦电容充电,并将其输送到功率晶体管的栅极电容,电流从功率晶体管的源极返回到去耦电容。为了关断,栅极驱动器将栅极连接到源极以消除栅极上的电荷。高转换速度是高频操作的关键,栅极驱动器必须克服导通和关断环路的电阻和电感,以获得高频操作的高效解决方案。这意味着强大的(低电阻)驱动器和低环路电感。

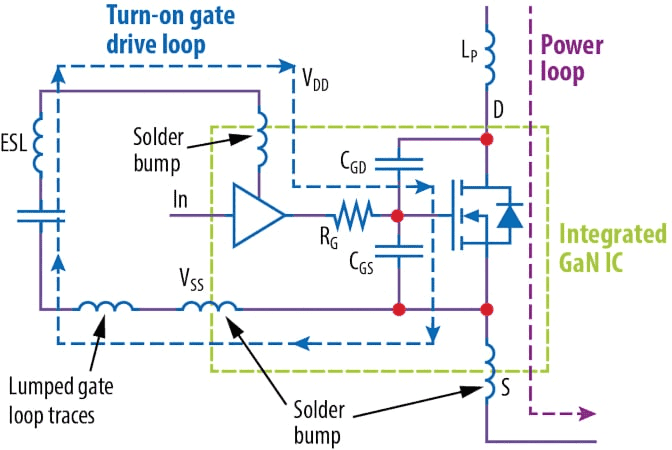

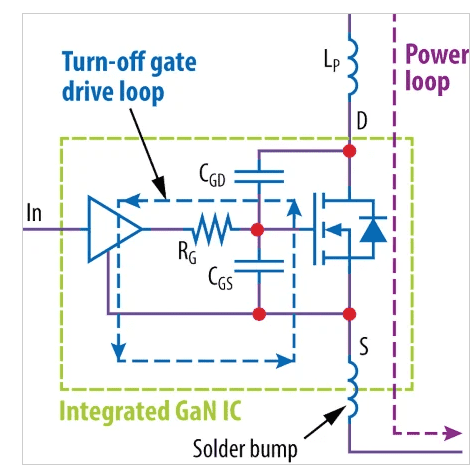

图 2 显示了电源模块分立解决方案的开 (a) 和关 (b) 栅极驱动环路及其杂散电感。杂散电感来自走线和互连,例如引线键合、焊料凸块和PCB走线。 GaN 器件是横向的,所有 电气 连接都位于同一表面上,允许使用焊料凸块进行晶圆级封装。它们的电感远低于具有垂直结构的硅MOSFET所需的引线键合或夹子。具有栅极驱动器的 GaN 晶体管的分立实施,具有 电容器 等效串联电感 (ESL)、用于栅极驱动器 V 的焊料凸点或焊线 DD/5 SS,以及用于晶体管栅极和源极的功率焊料凸点,以及PCB 走线。这些电感会阻碍功率晶体管栅极电容的充电和放电,从而减慢开关速度并增加换向损耗。

特别值得关注的是共源电感 (L.CS)。这是栅极驱动器和 电源 回路所共有的电感。它由功率晶体管源极焊料凸点和分离点之前的任何源极 PCB 走线组成。良好的设计实践是将这些环路尽可能靠近 FET 源极分开。共源电感的影响是 L 上的电源环路 di/dt 感应电压。在导通期间从施加到功率晶体管的 VGS 中减去 CS(并在关断期间添加到 VGS),减去缓慢的电流换向和增加的开关损失[3][4]。

图片由 Bodo 电力系统提供

b.图片由博多动力系统提供

C。图片由 Bodo's Power Systems 提供

d.

图2.

功率阻塞栅极驱动环路:(a) 分立导通,(b) 分立关断,(c) 集成氮化镓导通,(d) 集成氮化镓关断。图片由 Bodo 电力系统提供

考虑激光雷达激光驱动器等需要在 100 ns 内打开 1 A 电流的应用。基础电子学告诉我们 V = L di/ dt。 50 pH L.CS 感测 5 V,在栅极驱动阻抗上留下 0 V 以打开功率晶体管,从而无法实现所需的 DI/dt。虽然这个例子是极端的,但在功率转换和电机驱动应用中,现实生活中的共源电感对电流换向时间有很大的影响。电流换向时间由公式 1 估算,其中电流换向所需的栅极电荷由 (QGS, pg(k)) 给出,RG 是集总栅极驱动阻抗,VGS 是支持换向电源所需的电流晶体管栅极驱动电压,VDD为栅极驱动电压。

t=ZG(QGS−QG(TH))+LCSIDVDD−VGS(1) 当前换流时间

E=t*ID*D2 (2) 电流换流时间造成的能量损失

P=E*fP=E*f

(3)电流换流时间造成的功率损耗

例如,考虑 EPC2088 [5] 硬通、50 MHz 时换向 25 V、1 A。 GS = 4.4 nC,Q g(k) = 3.2 nC,ZG = RG (0.4 Ω) 加 0.7 Ω 栅极驱动器电阻(忽略栅极驱动环路电感),VDD = 5 V,V GS @ 25 A = 2.3 V,L .CS = 100 pH。等式 1 的 ZG 项给出的换向时间为 t = 600 ps。 L.CS 项导致电流换向时间为 1.14 ns。在此示例中,65% 的电流换向时间是由于共源电感造成的。使用公式 2 和公式 3,每个周期切换 710 A 和 25 V 时会损失 50 μJ 的能量,在 710 MHz 下使用共源电感仅消耗 1 mW 的功率。显然,必须最小化共源电感,以实现减小尺寸和提高频率的系统优势。

剩下的栅极驱动环路电感对开关损耗有更直接的影响,因为它们是RLC环路,电阻和电感会阻碍栅极电容的充电,如果电感太大,必须添加电阻来控制栅极过冲和振铃,进一步增加换向损耗。公式 4 显示了栅极环路临界阻尼所需的电阻,其中 RG(on) 是总导通栅极环路电阻,LG(on) 是导通栅极环路电感,Lcs 是共源极电感,CGS (on) 是换向电压下的 FET 栅源电容 [4]。由于时间、能量和功率与共源电感呈线性关系,因此高频功率转换需要特别注意封装和布局。

RG(on)≥√4×(LG(on)+LCS)CGS(on)��(��)≥4×(��(��)+����)���(��)(4 ) 临界阻尼所需的电阻

考虑功率晶体管与栅极驱动器集成的集成电路。这种集成消除了导通(图 2(c))和关断(图 2(d))栅极驱动路径中的所有外部共源电感,从而通过IC 设计人员电感最大限度地减少内部共源电感。精心放置 VDD 和 VSS 端子 有助于系统设计人员最大限度地减少迹线电感,从而使电容器等效串联电感 (ESL) 以及 VDD 和 VSS 焊料凸点成为导电栅极驱动器环路电感的唯一重要来源。一个关断栅极驱动环路,所有电感都将包含在 IC 内,使其达到绝对最小值。

除了减少栅极环路和共源极电感之外,将栅极驱动器与功率晶体管集成还提供了将栅极驱动器与功率晶体管匹配以获得最佳驱动强度的机会。示例包括 EPC21601(单端 40 V)、EPC21603(LVDS 40 V)和 EPC21701(单端 100 V)。

图3.

EPC23102 的功能框图。图片由 Bodo 电力系统提供

这些 GaN IC 专为需要在大于 15 MHz 的频率下进行 100 A 开关的间接飞行时间而设计。

GaN 集成增强

GaN 集成增强功能的示例包括 EPC 的 ePower 级 IC,例如 EPC23102[6]。这些 IC 配置为半桥,集成了全功能栅极驱动器,包括电平转换器、加电复位、交叉保护和延迟匹配。 ePower 级 IC 的功能框图如图 3 所示。这些 IC 专为各种应用而设计,范围从频率介于 10s 和 100s kHz 之间的电机驱动器到高频DC-DC 转换器,频率高达 3 MHz。在此频率范围内,必须控制开关速度而不影响核心栅极驱动性能。

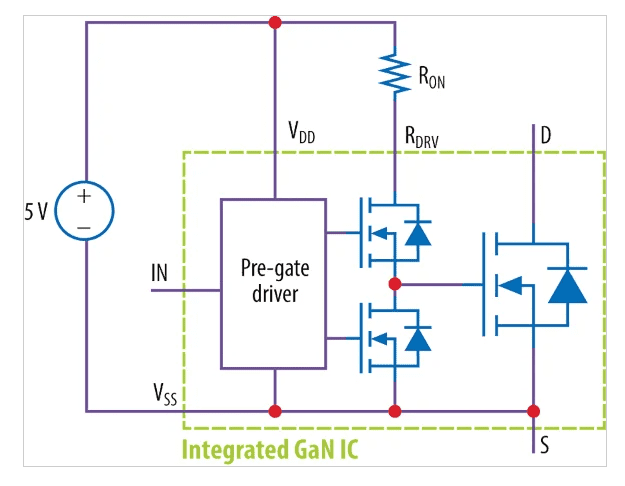

GaN 集成的主要优点之一是在栅极驱动器的输出级中使用 N 沟道 FET。使用 N 沟道 FET 驱动功率 FET 的导通,可以通过电阻控制导通来控制开关转换速率,从而控制过冲和振铃。这是控制 EMI 的重要因素,并且可以在不影响栅极驱动器其他特性的情况下实现。带栅极驱动器的集成功率 FET 的功能框图如图 4(a) 所示。

图片由 Bodo 电力系统提供

b.

图4.

(a) GaN 集成功率级的功能框图,(b) EPC48 开关节点在 9177 V 输入、10 A 输出、R = 2.2 Ω 时开启。图片由

提供Bodo 的动力总成提供

EPC9177 [7] 是一款使用 EPC23102 的开环半桥开发板。当R为2.2Ω时,在48V和10A下,导通开关节点波形得到很好的控制,如图4(b)所示。减少开关节点振铃对于控制 EMI 至关重要。

GaN 集成结论

GaN 集成为许多高频应用提供了许多系统优势。集成降低了栅极驱动电感和共源电感,提供快速的电流换向速度。它允许调谐换向以减少开关节点中的过冲和振铃,这对于 EMI 控制至关重要。它通过减小组件尺寸和提高频率来减小系统尺寸和成本。 GaN 集成减少了元件数量,降低了系统成本和尺寸,同时降低了供应链成本。 GaN 集成才刚刚开始,其优势肯定会随着时间的推移而增加。

报价

[1] Lidow, Alex, de Rooij, Michael, Strydon, Johan, Reusch, David 和 Glaser, John,《用于高效功率转换的 GaN 晶体管》,第 3 版,John Wiley & Sons Ltd,2020 年,第 2-5 页。

[2] Lidow, Alex,GaN 功率器件和应用,第 1 章,高效功率转换,2022 年,第 14 页。 16.

[3] Lidow、Alex 和 Strydom、Johan,eGaN FET 驱动rs 和布局考虑,2016 年。

[4] Lidow, Alex, de Rooij, Michael, Strydon, Johan, Reusch, David 和 Glaser, John,《用于高效功率转换的 GaN 晶体管》,第三版,John Wiley & Sons Ltd,2020 年,第 41 - 54 页。

[5] EPC2088 数据表 - 2022。

[6] EPC23102 数据表 - 2023。

[7] EPC9177 开发板快速入门指南 - 2023。

审稿编辑黄宇